LTspiceの一部回路の部品化、階層化によるブロック化し利便性を高める(1)回路の一部を特定の機能をもったコンポーネント化してブロック化する

大規模回路の中の、特定の機能をもった回路の部分をブロック化して回路図をよりわかりやすくします。または、OPアンプや電源などのような特定の機能をもった回路も、入出力と機能を明確にしてブロック化すると、新しい機能をもったデバイスのように扱うこともできます。

●Hierarchy(階層)

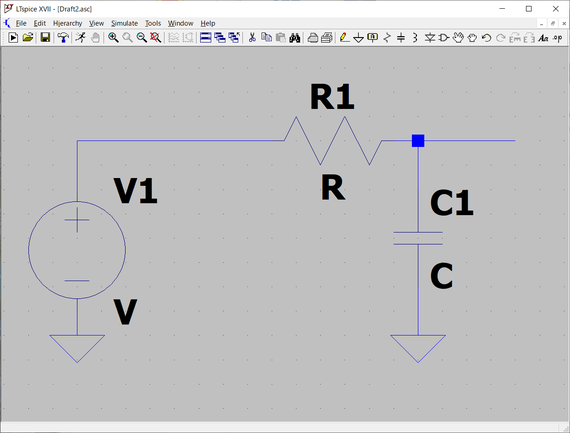

LTspiceXVIIのHelpにある目次の中の「LTspiceXVII」-「Hierarchy」で説明されている内容に従い、新しい回路モジュールを作成します。Helpの例では、トランジスタによる増幅回路を例に説明しています。ここでは、次に示すローパス・フィルタのCR回路を題材とします。

次の回路には、CRのフィルタの特性をチェックするための信号源としてV1のvoltageが追加されています。階層化の手順は次のようになります。

●ブロック化する回路の入出力端子にラベルを付ける

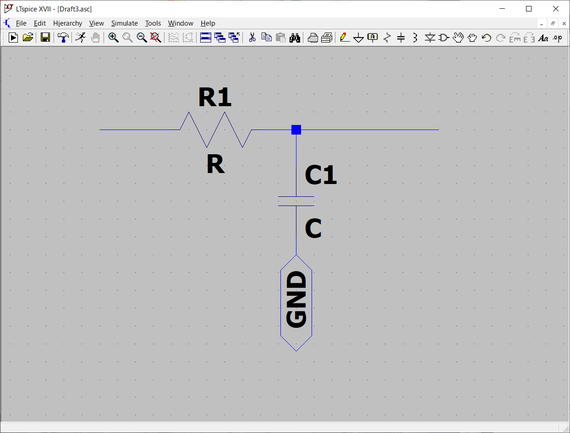

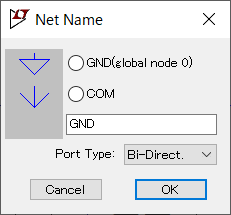

Label Netのアイコンをクリックして、次のラベルの設定を表示します。C1のGND側の端子のラベル名はGNDにし、入力欄にGNDをセットします。Port Typeは Bi-Direct(bidirectional;双方向)にします。

OKボタンをクリックすると、次に示すようにラベルが追加されます。

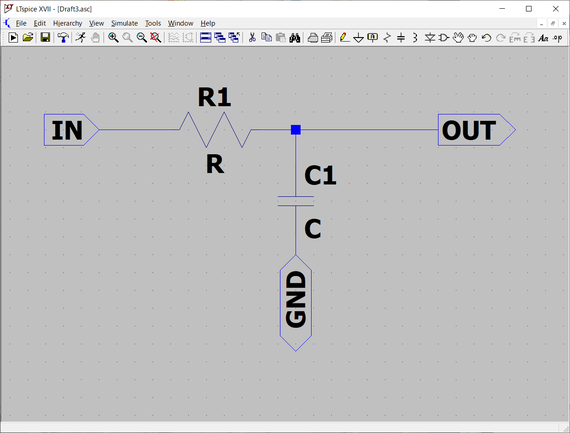

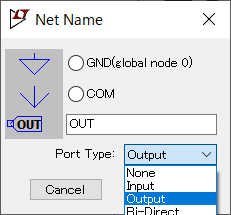

出力のラベルは次に示すようにポート名をOUTとして、Port TypeをOutputにします。

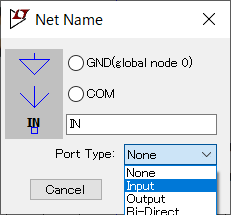

入力のラベルは次に示すようにポート名をINとして、Port TypeをInputにします。

ラベルの設定をすると、次に示すように各入出力ポートにラベルが設定されます。

●抵抗値とコンデンサの容量の設定

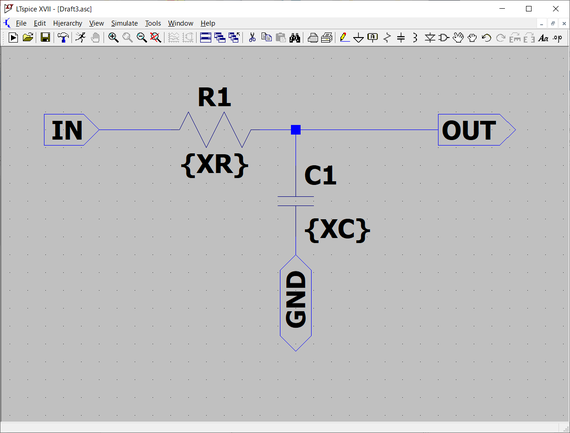

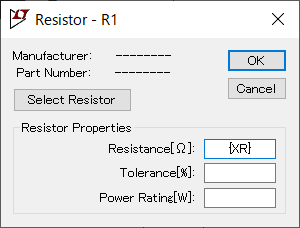

抵抗値とコンデンサの容量は、パラメータとして変化させたりなどするために変数として定義します。回路図の抵抗のシンボルをマウスの右ボタンでクリックすると、抵抗の特性値を設定する画面が表示されます。Resistance の入力欄に変数XRをセットするために{XR}を入力します。

●コンデンサの場合

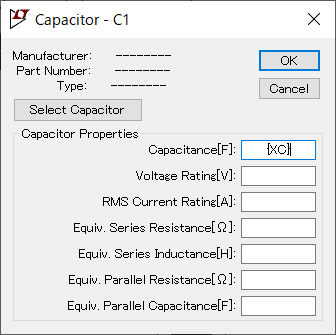

C1のコンデンサの容量の設定も、変数としてXCを設定します。C1のコンデンサのシンボルをマウスの右ボタンでクリックして、次のコンデンサの特性値の設定画面を表示します。

Capacitanceの入力欄に{XC}を入力します。

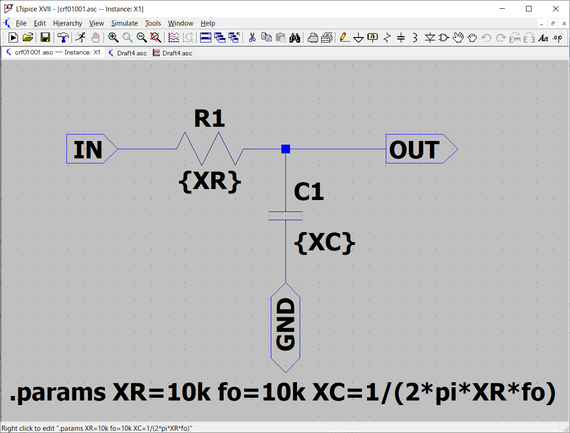

デバイスの特性値を変数として設定すると、回路図は次に示すようになります。このままでは、変数の値は設定されていないので、シミュレーションは行えません。 .param コマンドで各パラメータの値を決めます。

フィルタの仕様を決めるときの一番のめやすはカットオフ周波数となります。そのため、カットオフ周波数 fo と 抵抗値 XRの値を決めて、XCの値は fo とXRから次の式で求めます。

| fo = 1 / (2πXR × XC) XC = 1 / (2πXR × fo) .params XR=10k fo=10k XC=1/(2*pai*XR*fo) |

と .paramsコマンドを次のように設定しました。

●ブロックの回路図をもとにブロックのシンボルを作る

シンボル・ファイル・エディタでゼロからシンボルを作る方法もあります。しかし、回路図から自動でシンボルを作ることができます。

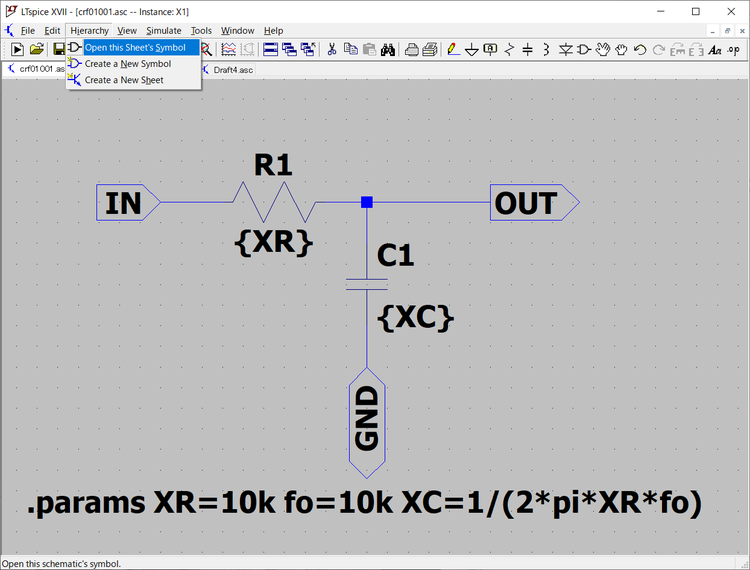

●シンボル・ファイルを作る

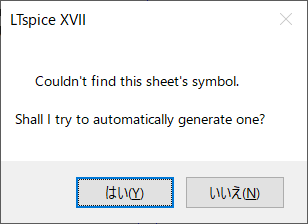

次に示すメニュー・バーのHierarchyをクリックして、Open this Sheet’s Symbol を選択します。

次に示すように、このシートのシンボルが見つかりません、これをこのファイルのデータから作成しましょうかと聞いてきます。

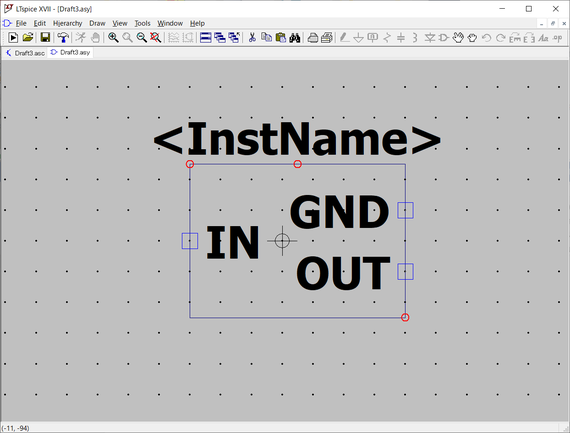

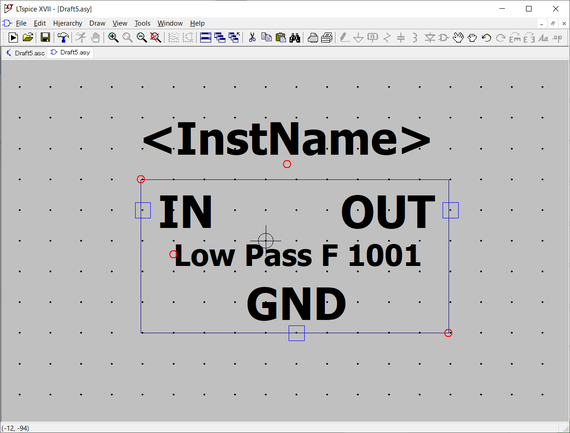

「はい」で答えると、次に示すようにシンボル・ファイルが作成されます。

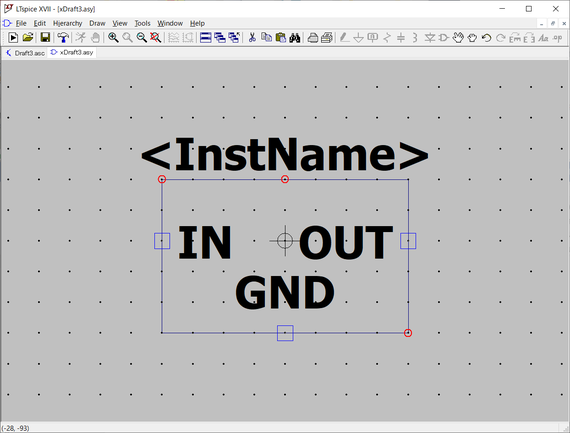

作成されたシンボルはGNDが上にあるので、底辺の真ん中になるように修正します。

GNDのポートの移動は、ツール・バーの大きい手のマーク moveアイコンを選択し、マウス・ポインタの形状もmoveアイコンにして、GNDの表示をクリックして移動先までドラッグします。IN、OUTは上部に移動してそろえます。

枠の大きさの修正は、ツール・バーの小さい手のアイコンのDragを選択して行います。

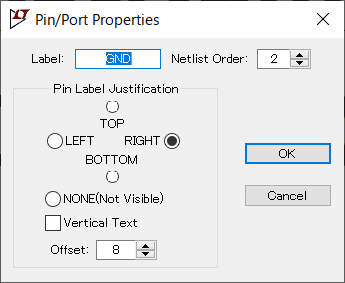

GNDの表示をマウスの右ボタンでクリックすると、次に示すPin/Port Propertiesの確認設定画面が表示されます。

Pin Label Justificationでは、四角ピンのマークとラベルの位置関係を設定します。表示はラベルを基準にしたピンの位置です。しかし、この設定を変えると四角いピンの位置は変わりませんが、ラベルの位置が変わります。

基本的な枠組みはできましたが、このブロックがなんであるか示されていません。メニュー・バーの、

| Draw > Text |

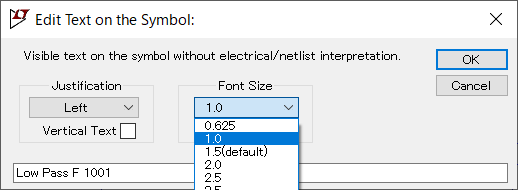

を選択すると、シンボルにテキストを表示するための画面が表示されます。テキストとして「Low Pass F 1001」と設定しました。Font Sizeはデフォルトの大きさではエリアに入らないので1.0に変更しました。

外枠も少し広げてあります。四角の外枠の角の赤丸を小さい手のDragのアイコンを選択しマウスでクリックすると赤丸は黒丸になり、ドラッグすると図形の伸長、短縮ができます。

ポートとラベルのオフセットを調節することができます。ラベルまたはポートをマウスの右ボタンでクリックすると、次の設定画面が表示されます。この中のoffsetを、デフォルトの8から2に変更しています。上記のGNDはこの設定を行っています。

●ブロックのファイルの保存

作成したブロックのシンボル・ファイルを保存する必要があります。このブロックを回路図に取り込むときは、コンポーネントの取り込みと同じ方法を用います。そのため、LTspiceのライブラリのsymフォルダの下にmylibという新しいフォルダを作り、そのフォルダにブロックのシンボル・ファイル、回路図ファイルを保存します。

メニュー・バーの、

| File >Save As |

を選択して、新しく作成したmylibフォルダにcrf1001.ascとcrf1001.asyを保存します。

●作成したブロックのテスト

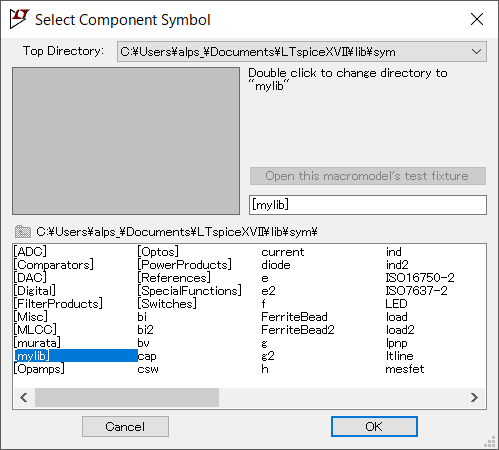

作成したブロックの動作確認を行います。LTspiceの回路図の作成画面にして、ツール・バーのコンポーネントのアイコンを選択し、次のコンポーネントを選択します。

ブロックのファイルはmylibに格納したので、上記に示したように[mylib]を選択すると次の画面が表示されます。

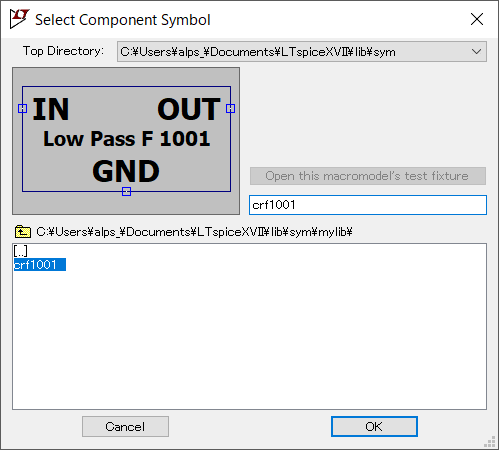

先ほど作成したcrf1001を選択すると、次に示すように回路図の画面のブロックのシンボルが表示されます。このシンボルに対して回路を付加していきます。

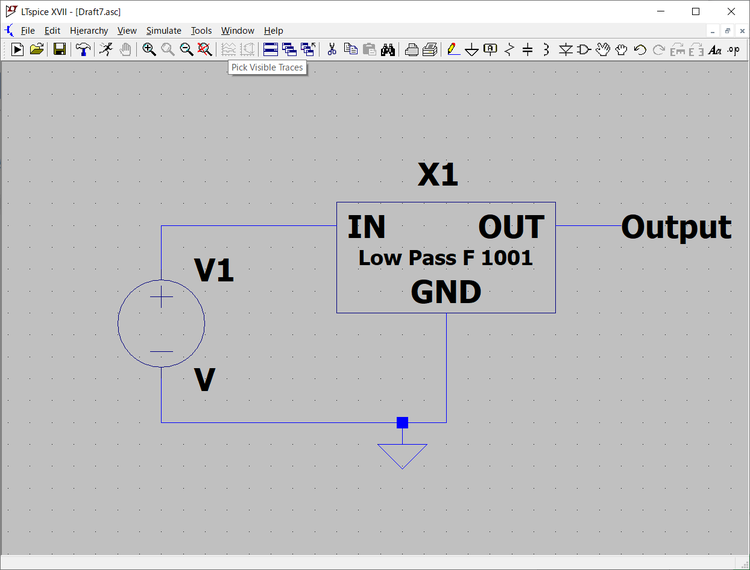

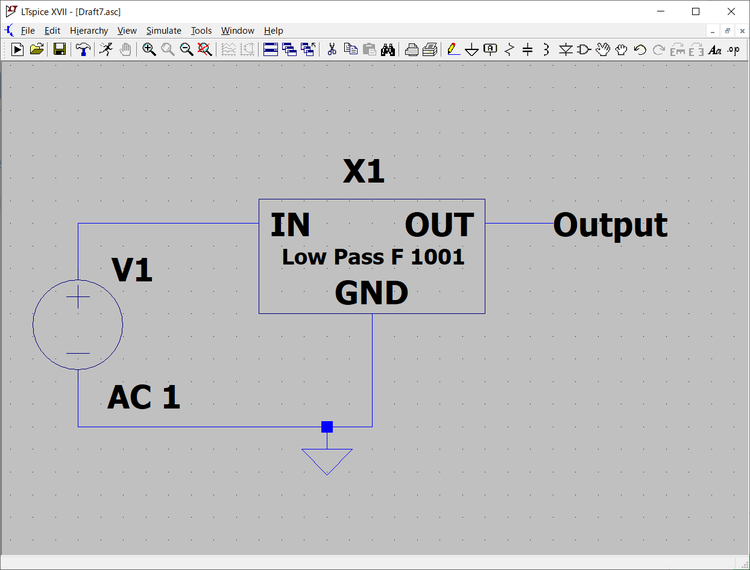

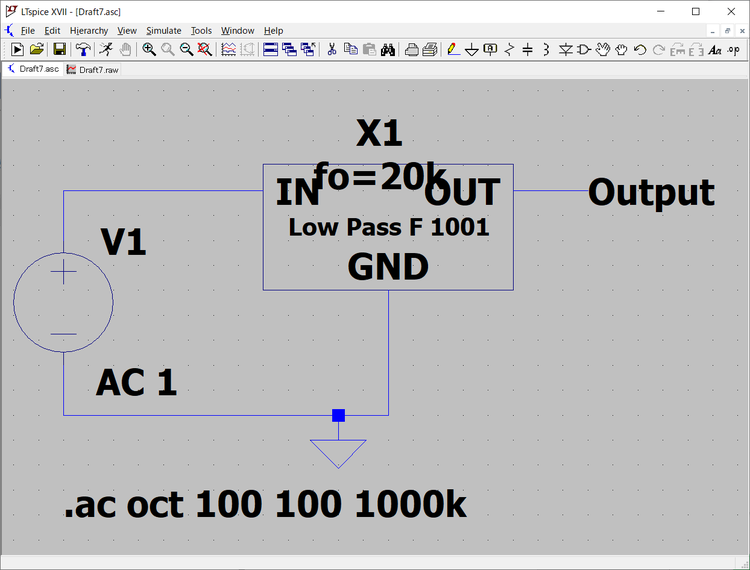

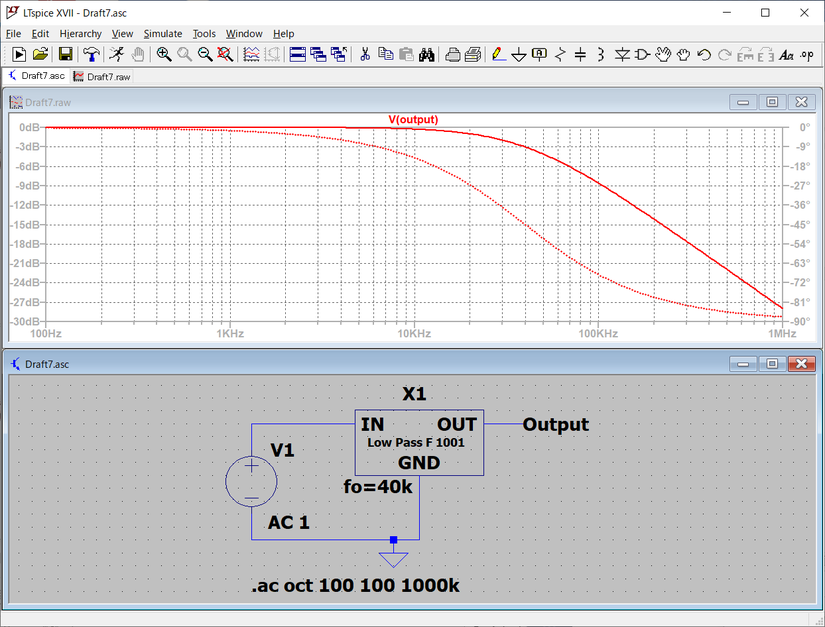

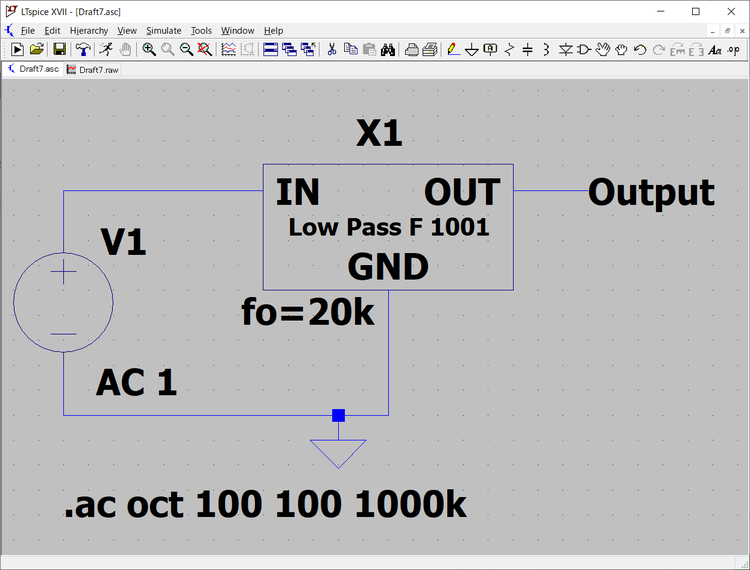

このブロックとV1のvoltageは電源を必要としません。そのため、信号源(voltage)と基準となるGNDを追加するだけで、回路は完成します。次の回路には出力のポイントをわかりやすくするためのラベルoutputを追加しています。

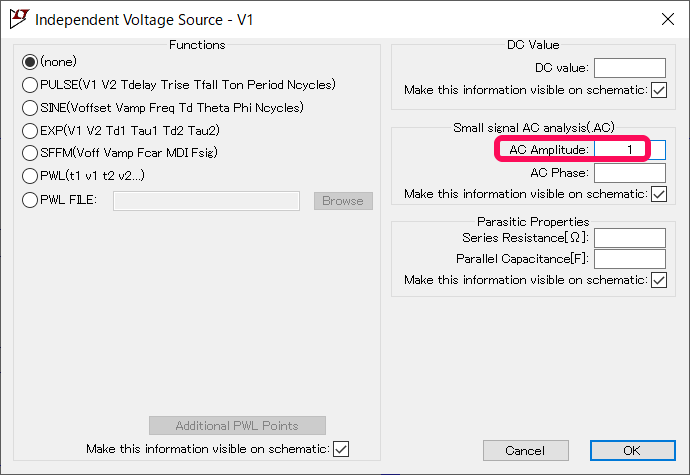

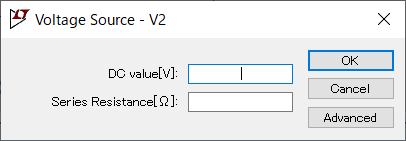

V1のvoltageのシンボルをマウスの右ボタンでクリックして、次の画面を表示してadvancedを選択します。

次のvoltageの仕様の詳細を設定する画面を表示します。各種の信号を生成することができます。今回はAC特性のテストのみなので、Small signal AC analysis(AC)の欄に1を入力します。これで、AC解析の入力信号がピーク値±1の正弦波となります。

信号源の準備完了した回路図は次のようになります。

●AC解析の設定

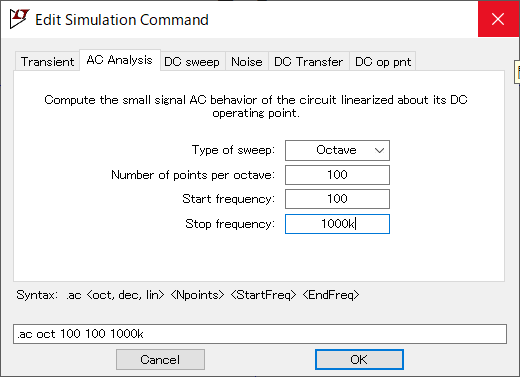

メニュー・バーのSimulate>Edit Simulation Cmdを選択して、Edit Simulate Commandの画面を表示します。AC Analysisのタグをクリックして次に示す画面を表示し、スイープ・タイプをOctave、オクターブ当たりのシミュレーション・ポイントを100、開始周波数100Hz、終了周波数を1000kHzと設定しました。

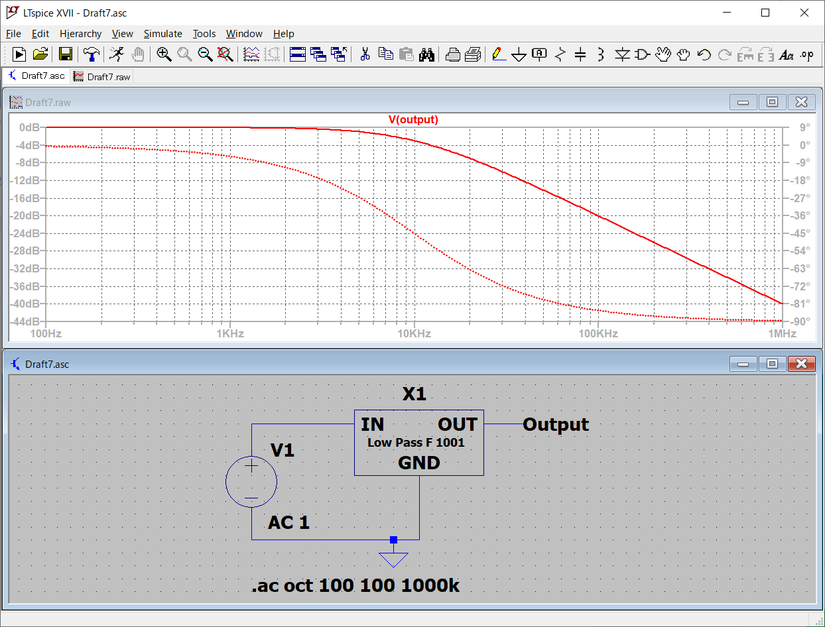

シミュレーション結果は次のようになりました。カットオフ周波数10kHzでは-3dBの値で、想定通りの結果となりました。

●ブロック内のパラメータを変更する

ブロック化された回路内で利用しているパラメータの値を、ブロックを利用している回路で変更してシミュレーションできます。

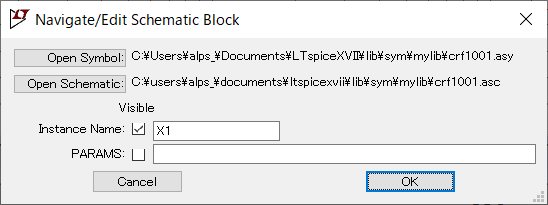

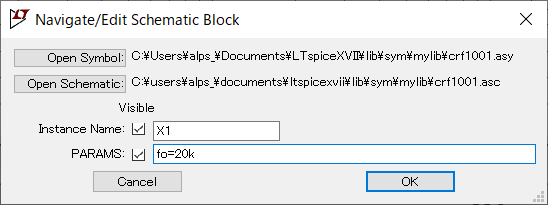

ブロックのシンボルをマウスの右ボタンでクリックすると、次に示すブロック内の回路の処理を行うための画面が表示されます。今回は、パラメータの値を変更します。ブロックの回路図ファイル、シンボル・ファイルを開くこともできます。

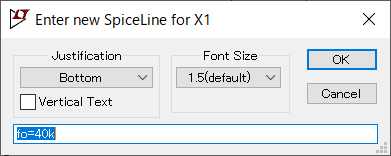

PARAMSの入力欄に、カットオフ周波数を20kHzにするための fo=20k と次のように設定します。Visibleをチェックすると、シンボルと共に入力欄の値が表示されます。

fo=20kの表示が、シンボルのほかの項目の表示と重なっています。ツール・バーのMoveを選択して移動します。

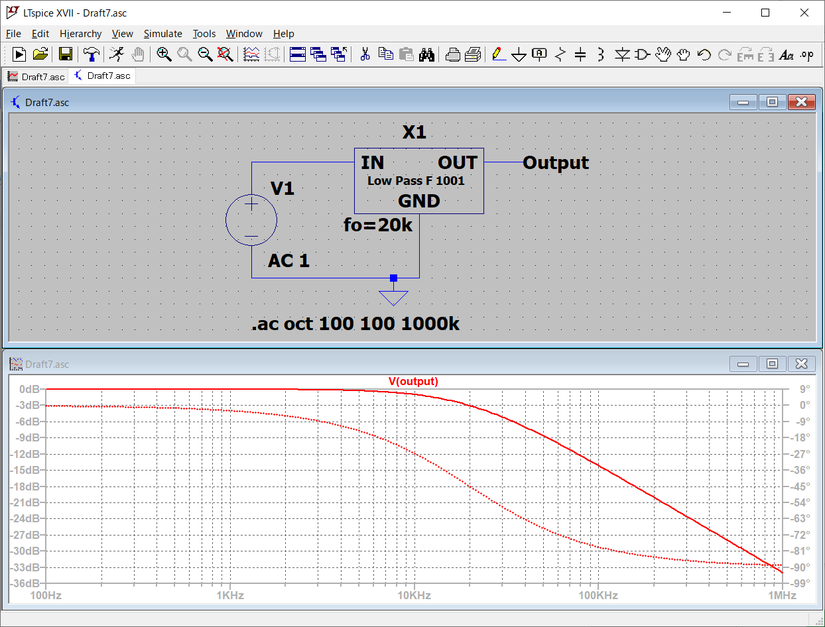

fo=20kの表示を移動してみやすくなりました。

シミュレーション結果は次のようになりました。カットオフ周波数は20kHzになっています。

追加された fo=20k の文字をマウスの右ボタンでクリックすると、次に示す文字表示の編集を行う画面が表示されます。文字が大きい場合は、デフォルトの1.5から1に表示します。

また、表示の fo=40k とパラメータを任意の値に変更できます。

変更した結果を次に示すようになりました。カットオフ周波数は40kHzとなり、設定どおりとなります。

次回は、もう少し複雑な回路をブロック化してみます。

(2020/4/28 V1.0)

<神崎康宏>